基于JTAG的ARM芯片系統調試

隨著嵌入式處理器性能的逐步提高,運算速度越來越快、處理的數據量越來越大,傳統的調試方法如ROM駐留監控程序以及串口調試工具已經不能滿足要求。ARM處理器采用一種基于JTAG的ARM的內核調試通道,它具有典型的ICE功能,基于ARM的包含有Embedded ICE(嵌入式在線仿真器)模塊的系統芯片通過JTAG端口與主計算機連接。通過配置支持正常的斷點、觀察點以及處理器和系統狀態訪問,完成調試。為了對代碼進行實時跟蹤,ARM的提供了嵌入式跟蹤單元(Embedded Trace Macrocell),對應用程序的調試將更加全面。 2 JTAG邊界掃描原理 “JTAG邊界掃描”或IEEE1149標準[1]是由“測試聯合行動組”(Joint Test Action Group,簡稱JTAG)開發的針對PCB的“標準測試訪問接口和邊界掃描結構”的標準。這個標準是ARM處理器調試的基礎。 2.1 硬件電路 JTAG邊界掃描測試接口的一般結構[2]如圖1所示。 JTAG邊界掃描硬件電路主要由三部分構成: 1) TAP控制器。測試訪問端口(TAP)控制器,是由TMS控制狀態轉換的狀態機。 2) 指令寄存器。用于存儲JTAG邊界掃描指令,通過它可以串行的輸入并執行各種操作指令。 3) 數據寄存器。特定芯片的行為由測試指令寄存器的內容決定。測試指令寄存器可用來選擇各種不同的數據寄存器。 2.2 邊界掃描測試信號 支持這個測試標準的芯片必須提供5個專用信號接口: ? TRST:測試復位輸入信號,低電平有效,為TAP控制器提供異步初始化信號。 ? TCK:JTAG測試時鐘,獨立于任何系統時鐘,為TAP控制器和寄存器提供測試參考。 ? TMS:TAP控制器的測試模式選擇信號,控制測試接口狀態機的操作。 ? TDI:JTAG指令和數據寄存器的串行輸入端,給邊界掃描鏈或指令寄存器提供數據。 ? TDO:TAG指令和數據寄存器的串行輸出。 2.3 指令 JTAG測試系統是通過向指令寄存器送入指令,然后使用數據寄存器進行測試。測試指令說明要進行的測試種類及測試要使用的數據寄存器。測試指令分為公開指令和私有指令。公開指令已經定義且用于通用測試。私用指令用于片上的專用測試,測試標準沒有規定如何使用私有指令。測試標準支持的最小集的公開指令有: ? BYPASS:器件將TDI經一個時鐘延時連接到TDO,用于同一個測試環中其它器件的測試。 ? EXTEST:將邊界掃描寄存器連接到TDI和TDO之間,用于支持板級連接測試。 ? IDCODE:將ID寄存器連接到TDI和TDO之間。通過它可以讀出器件ID(廠家賦與的固定標識,包括產品編號及版本碼)。 ? INTEST:將邊界掃描寄存器連接到TDI和TDO之間。 3 EmbeddedICE ARM的EmbeddedICE調試結構[3]是一種基于JTAG的ARM的內核調試通道,它是基于JTAG測試端口的擴展,引入了附加的斷點和觀測點寄存器,這些數據寄存器可以通過專用JTAG指令來訪問,一個跟蹤緩沖器也可用相似的方法訪問。ARM核周圍的掃描路徑可以將指令加入ARM流水線并且不會干擾系統的其它部分。這些指令可以訪問及修改ARM和系統的狀態。由于EmbeddedICE條件斷點,單步運行等功能的實現是基于片上JTAG測試訪問端口進行調試,芯片不需要增加額外的引腳,避免使用笨重的、不可靠的探針接插設備完成調試。芯片中的調試模塊與外部的系統時序分開,可以直接運行在芯片內部的獨立時鐘速度。 3.1 硬件結構 EmbeddedICE模塊包括兩個觀察點寄存器和控制與狀態寄存器,還包括一個Debug comms端口。當地址、數據和控制信號與觀察點寄存器的編程數據相匹配時,也就是觸發條件滿足時,觀察點寄存器可以中止處理器。由于比較是在屏蔽控制下進行的,因此當ROM或RAM中的一條指令執行時,任何一個觀察點寄存器可配置為能夠中止處理器的斷點寄存器。 1) 觀察點 每個觀察點皆可以觀察ARM地址總線、數據總線、和 等信號的特定組合值。任何一個組合值與觀察點寄存器值匹配則中止處理器。另外一種方式是把兩個觀察點鏈接起來,只有第一個觀察點先匹配了,當第二個觀察點再匹配時將使處理器中止。 2) 寄存器 EmbeddedICE寄存器通過JTAG測試端口使用專用掃描鏈編程。掃描鏈38位長,包括32個數據位,5個地址位和一個控制寄存器是讀還是寫的 位。地址位指定特定的寄存器,地址和寄存器一一對應。 3) Debug comms端口 debug comms端口運行在目標系統上的軟件可以通過這個端口與主機通信。運行在目標系統上的軟件將comms端口視為一個6位控制寄存器和32位可讀寫寄存器,可以使用對協處理器14的MRC和MCR指令訪問。主機將這些寄存器視為EmbeddedICE寄存器。 3.2 實現原理 1) 訪問狀態 EmbeddedICE模塊允許程序在指定點中止,但不允許直接觀測、修改處理器或系統狀態。這可以通過屬于JTAG端口訪問的掃描路徑實現。訪問處理器狀態的方法是中止處理器,再在處理器指令序列中強制插入一條多寄存器存取指令。然后通過掃描鏈向處理器加入時鐘,使處理器將寄存器內容送到數據端口。每個寄存器的值都可以被掃描鏈采樣并移出。 2) 調試 基于ARM的包括EmbeddedICE模塊的系統芯片通過JTAG端口和協議轉換器與主計算機連接。這種配置支持正常的斷點、觀察點以及處理器和系統狀態訪問,(除上面介紹的comms端口以外)這是程序設計人員在本地或基于ICE的調試中習慣采用的方式。采用適當的主機調試軟件,以較少的硬件代價得到完全的源代碼級調試功能。 4 ARM的嵌入式跟蹤 EmbeddedICE提供的斷點及觀察點將使處理器偏離正常執行序列,破壞了軟件的實時行為,它不能完成實時操作調試功能。ARM結構的處理器采用嵌入式跟蹤宏單元ETM很好的解決了系統實時調試的問題。 4.1 硬件電路 EmbeddedICE單元支持斷點和觀察點功能并提供主機和目標軟件的通信通道。ETM單元[5]壓縮處理器接口信息并通過跟蹤端口送到片外。這兩個單元都由JTAG端口控制。SoC外部的EmbeddedICE控制器用于將主機系統連接到JTAG端口,跟蹤端口分析器使主機系統與跟蹤端口對接。主機通過一個網絡可以與跟蹤端口分析器和EmbeddedICE二者連接。 4.2 實現原理 由調試軟件配置并通過標準JTAG接口傳輸到ETM上。在程序執行時ETM可以通過產生對處理器地址、數據及控制總線活動的追蹤(Trace)來獲得處理器的全速操作情況。在實時仿真時外設和中斷程序依然能夠繼續運行。用戶控制斷點和觀察點的設置并可以配置各種跟蹤功能。跟蹤觸發條件可以指定,跟蹤采集可以在觸發之前、之后或以觸發為中心可以選擇跟蹤是否包括數據訪問。跟蹤采集可以是數據訪問的地址、數據本身,也可以是兩者兼有。 ETM是使用軟件通過JTAG端口進行配置的,所使用的軟件是ARM軟件開發工具的一個擴展。跟蹤數據從跟蹤端口分析儀下載并解壓,最終反鏈接到源代碼。 5 應用實例 下面以S3CEV40開發板[4]為例,介紹ARM調試結構應用。S3CEV40采用的CPU為Samsung公司的S3C44B0X,是國內應用廣泛的基于ARM7TDMI內核的SoC。其調試系統的硬件結構如圖2: 計算機的并行口和Embest PowerICE for ARM仿真器的DB25接口通過標準的DB25公、母轉換電纜連接。Embest PowerICE for ARM仿真器通過一個的IDC頭的直通電纜(1-1, 2-2,… 20-20)與目標板的JTAG接口相連接。20芯的Embest PowerICE for ARM仿真器接口的定義如圖3所示: S3CEV40所用到的調試軟件為EmbestIDE集成開發環境,它提供源碼級調試,提供了圖形和命令行兩種調試方式,可進行斷點設置、單步執行、異常處理,可查看修改內存、寄存器、變量等,可查看函數棧,可進行反匯編等。它為用戶提供2種調試方法: 脫機調試:Embest IDE for ARM帶ARM指令集模擬器,用戶能在PC上調試ARM應用軟件。 下載調試:Embest IDE將程序通過仿真器下載到開發板,直接進行調試。 Embest IDE的調試功能包括:斷點功能;程序的單步執行;變量監視功能,隨程序運行同步更新變量,變量值即時修改;寄存器即時查看與修改;存儲器查看與修改,存儲器內容顯示格式定制;堆棧顯示;同時提供圖形界面操作和命令行操作方式;支持被調試代碼的多種顯示模式,能以源碼、匯編、混合等形式來顯示程序;具有與MS Visual Studio類似的調試菜單功能:Go,Stop,Reset,Step into,Run to Cursor等;程序的上載和下載。 6 結束語 本文介紹了32位ARM嵌入式處理器的調試技術。在JTAG邊界掃描技術的基礎上介紹了ARM的EmbeddedICE及嵌入式跟蹤并在此基礎上介紹了一個系統調試實例。嵌入式調試技術是嵌入式軟硬件開發中必要的一環,掌握了它能在開發中起到事半功倍的作用。 嵌入式技術正在日新月異的發展著,嵌入式調試技術也不是一成不變的,它必將隨著高速、低功耗Soc的發展而進步。

提交

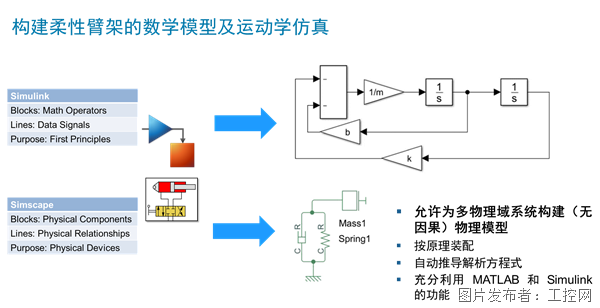

超越傳統直覺,MATLAB/Simulink助力重型機械的智能化轉型

新大陸自動識別精彩亮相2024華南國際工業博覽會

派拓網絡被Forrester評為XDR領域領導者

智能工控,存儲強基 | 海康威視帶來精彩主題演講

展會|Lubeworks路博流體供料系統精彩亮相AMTS展會

投訴建議

投訴建議